第一列

通用量子電腦硬體技術

矽基量子點量子計算理論

本計畫旨在為矽基量子點自旋量子位元之量子計算的實驗實現提供理論研究和描述。我們進行元件模擬以協助量子位元元件的設計和製造,並為量子閘建立控制脈衝以抵抗量子和古典雜訊以及系統參數不確定性,來達到具有容錯計算的保真度。我們積極與國內外團隊合作,嘗試將我們優化的控制脈衝施加在實際元件上,以實現高保真和穩健的量子閘。這些量子閘操作的成功實現將證實並使矽基量子點量子位元成為大規模量子計算的實用物理系統之一。

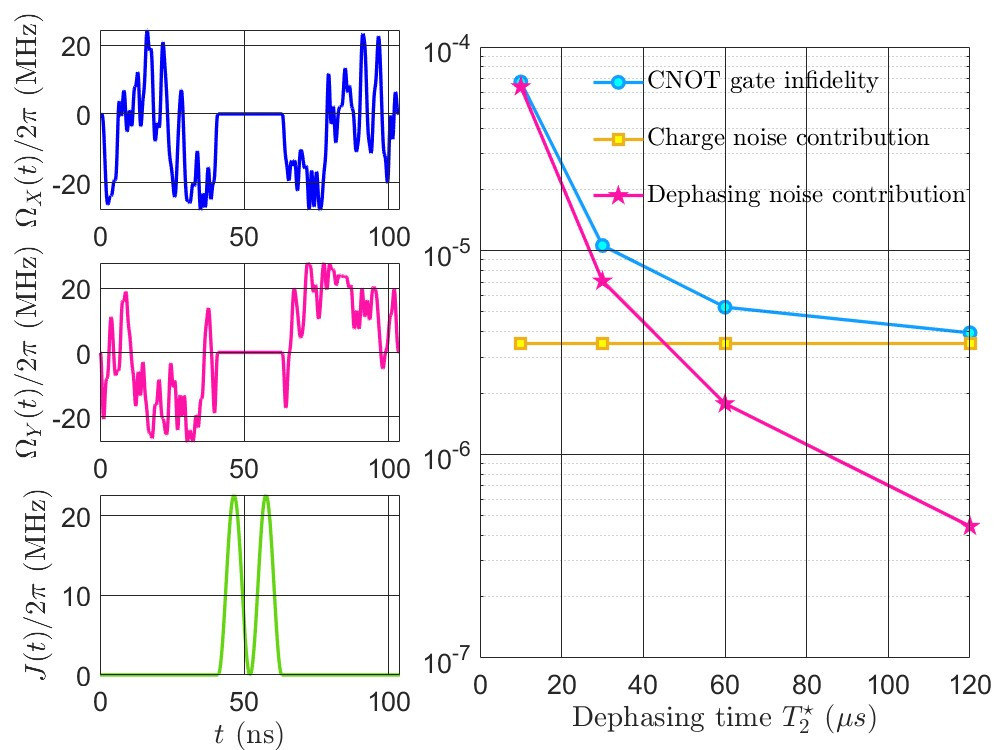

針對具有可調諧耦合的量子點自旋量子位元,藉由最佳化控制波形實現可抗拒電荷雜訊與去相位雜訊的高保真雙位元CNOT量子邏輯閘 (數值模擬)。

團隊成員

技術亮點

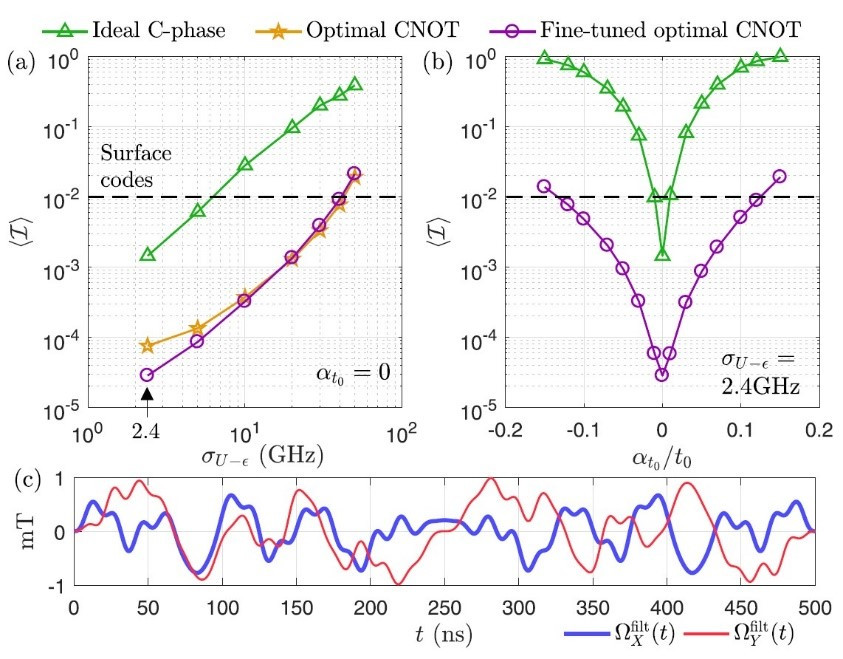

針對量子點自旋量子位元的高保真且穩健的雙位元量子邏輯閘控制

- 此技術欲解決問題:

提升量子邏輯閘的保真度,並增加邏輯閘容忍雜訊與系統參數不確定性的能力。 - 重要性/突破性:

此技術可有效降低邏輯閘誤差超過一個數量級,並同時大幅提升對雜訊與系統參數不準度的穩健性(robustness)。 - 與計畫未來研發方向的關聯性:

此技術將運用在實際元件上以實踐高保真且穩健的雙位元量子邏輯閘。並以此技術為基礎,擴展至多位元量子邏輯閘控制。

針對量子點自旋量子位元所建構的最佳化控制波形如圖(c)所示,可達成高保真且穩健的雙位元量子邏輯閘如圖(a)與(b)所示。

出處:PHYSICAL REVIEW A 99, 042310 (2019)

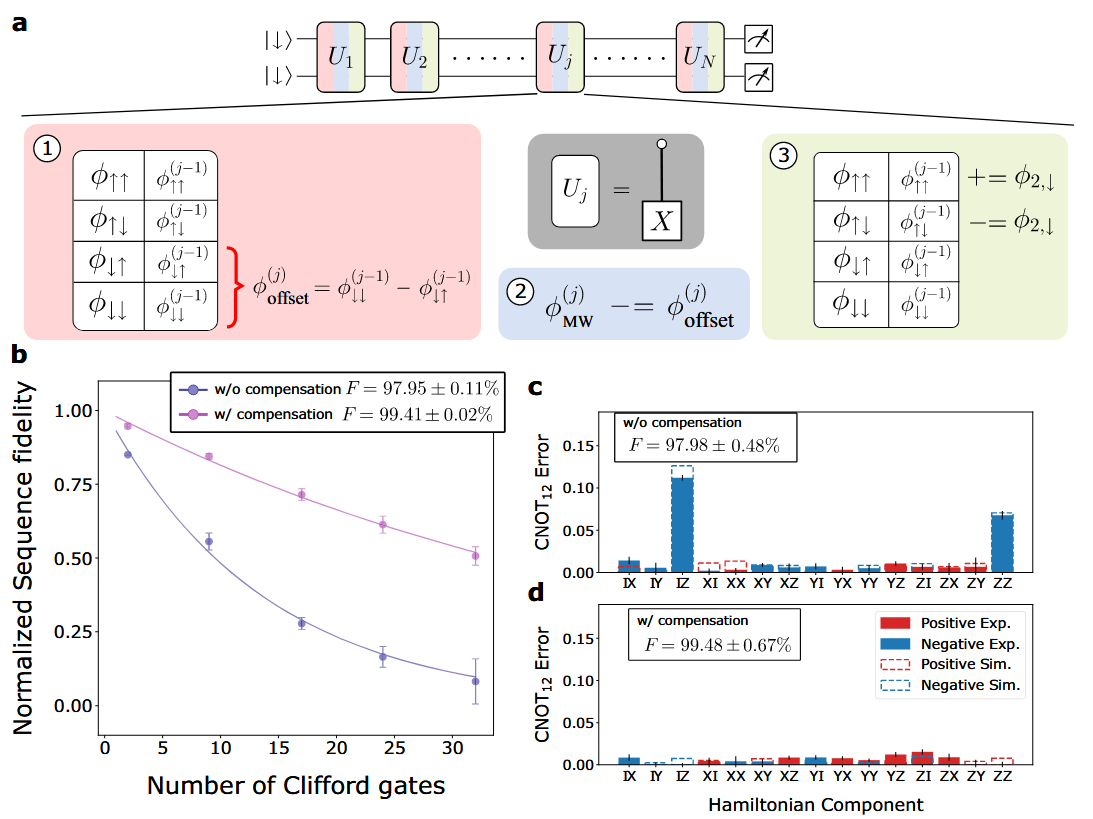

在超過容錯閾值的共振驅動CNOT量子閘中的哈密頓相位誤差

- 此技術欲解決問題:

提高雙量子邏輯閘的保真度達到99%以上以實現容錯量子計算。 - 重要性/突破性:

此方法能夠量測雙量子位元CNOT量子閘的相位誤差,並改變施加的微波訊號相位來修正誤差對保真度的影響。 - 與計畫未來研發方向的關聯性:

藉由了解雙量子位元CNOT量子閘的誤差來提高邏輯閘的保真度,此項誤差的技術也能夠應用在未來大規模的矽基量子電腦中。

圖 (a) 顯示了補償錯誤影響的程序。我們使用了一個記錄所有基態量子態上積累的相位誤差的表格來計算所需的相位偏移量。圖 (b) 和 (c) 顯示了基準測試實驗的結果,其中CNOT量子閘的保真度提高到了 99.5%。

出處:Wu et al., npj Quantum Information volume 10, Article number: 8 (2024)