第一列

通用量子電腦硬體技術

矽基自旋量子位元與CryoCMOS電路整合之CMOS製程相容量子處理器

本計劃的主軸為開發矽基半導體量子電腦的相關技術,包含與CMOS製程相容的高可靠度量子位元,操控及讀取量子位元的cryo-CMOS低雜訊、低功耗主動電路,以IPD (Integrated Passive Device)製程設計的被動電路,並整合量子位元與所需的主被動電路於IPD基板,達成微型化的目標,未來可進一步實現大規模的通用型矽基半導體量子電腦。

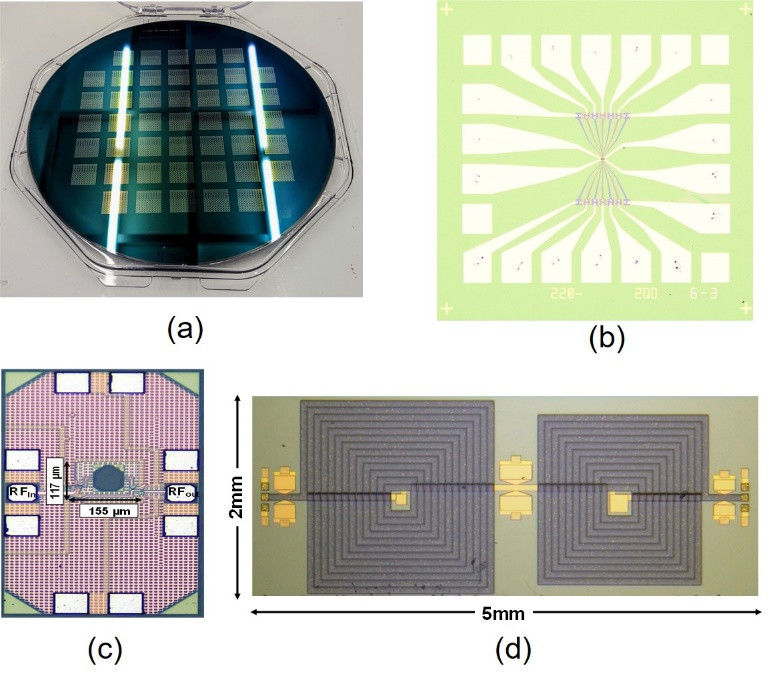

(a) 矽基量子位元製作於8-inch SOI晶圓。

(b) FinFET 量子位元的上視圖。

(c) Cryo-CMOS 低雜訊放大器晶片圖。

(d)微型化IPD濾波器晶片圖

團隊成員

-

共同主持人

-

張鑑元(國立清華大學電機工程學系)

-

蕭子綱(國立清華大學物理學系)

-

卓大鈞(財團法人國家實驗研究院台灣半導體研究中心)

技術亮點

用於量子位元讀取之微型化無電感雜訊消除Cryo-CMOS低雜訊放大器

- 此技術欲解決問題:

射頻/微波低雜訊放大器為量子位元讀取最重要的前端電路,此放大器需達到低雜訊溫度,低功率損耗,及微型化的規格。而目前的離散式低雜訊放大器無法達到這些要求。 - 重要性/突破性:

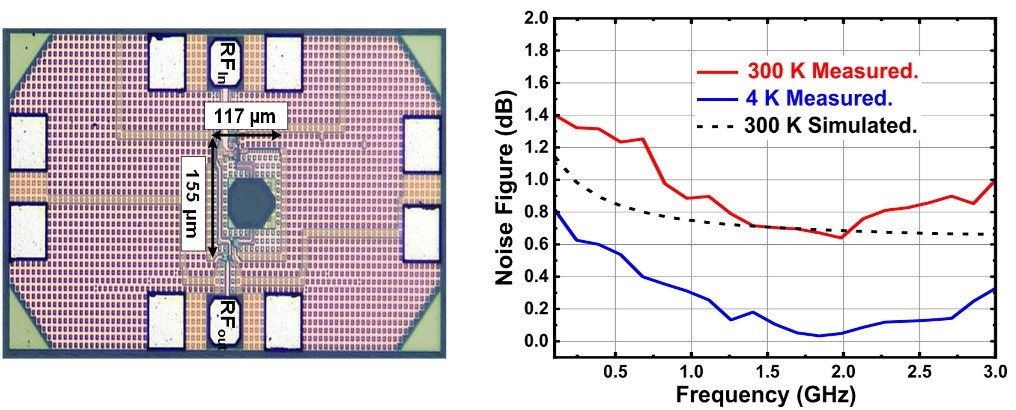

我們使用先進的CMOS製程,提出無電感雜訊消除的架構設計用於量子位元讀取的低雜訊放大器,量測結果最佳可達到2.2K的雜訊溫度,增益為29dB,頻寬可達到3GHz,功率消耗為19.4 mW,且晶片面積僅佔0.018mm2. - 與計畫未來研發方向的關聯性:

此微型化放大器可與本計畫的spin 量子位元整合,達成RF reflectometry量子位元的讀取。

左圖:微型化無電感雜訊消除Cryo-CMOS低雜訊放大器晶片圖

右圖:室溫及4K的量測及模擬雜訊特性

出處:M. K. Chaubey, Y. Liu, Y. Chang, P. Wu, H. Tsai, and S. S. H. Hsu*, “Ultracompact inductorless noise-canceling LNAs in 40-nm CMOS achieving 2.2-K noise temperature for qubit readout,” IEEE Trans. Microwave Theory Techn., vol. 72, no. 4, pp. 2168-2178, Apr. 2024