第一列

通用量子電腦硬體技術

利用低溫CMOS控制及讀取固態量子位元

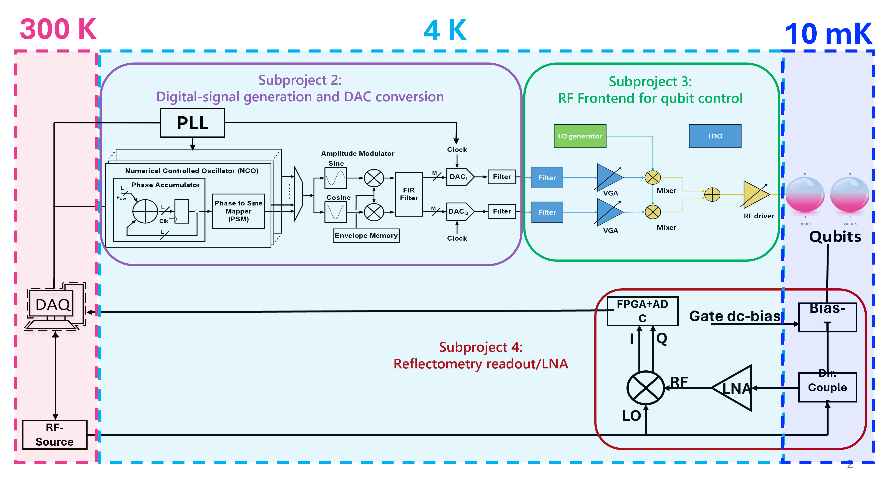

低溫固態量子處理器由室溫儀器存取量子位元,且需獨立線路操控,量子位元增加導致的複雜佈線限制大規模通用量子電腦發展,為解決佈線問題,我們以低溫CMOS系統單晶片存取超導體及半導體量子位元,4K操控晶片包含數位、數位類比介面及射頻前端模組;讀取晶片(20 mK至4 K)利用閘極反射法結合低雜訊放大器、類比數位轉換器和cryo-FPGA,縮短與量子位元的距離。為進一步改善信號品質,我們將利用雷射與光纖取代同軸電纜轉換量子訊息為光訊號。

圖片是以團隊計畫內容所設計。正中間的NTUEE表示團隊組成成員均為台大電機系所的教授與學生。紅藍漸層象徵著溫度從相對高溫(4K)至極低溫(20mK)的實際系統溫度漸變。左上置於4K溫度的Cryo-CMOS晶片,產生控制訊號並輸出至右下處於20mK環境的量子位元,接著再將量子位元狀態自20mK讀回至4K的CMOS系統單晶片,此一流程展現出計畫大意。

團隊成員

-

共同主持人

-

呂良鴻(國立臺灣大學電機工程學系)

-

陳士元(國立臺灣大學電機工程學系)

-

楊家驤(國立臺灣大學電機工程學系)

技術亮點

利用低溫CMOS控制及讀取固態量子位元

- 此技術欲解決問題:

低溫CMOS系統單晶片存取固態量子位元,可解決大規模量子電腦因繞線衍伸的熱、雜訊以及近乎不合理的成本問題。 - 重要性/突破性:

本計畫包含數位、數位類比介面及射頻前端等控制晶片模組,以及利用閘極反射法結合低雜訊放大器、類比數位轉換器和FPGA讀取量子位元信號。目前主要的突破在達成4 K下的30 GHz的VCO電路(信號提供)以及讀取端的低雜訊放大器。 - 與計畫未來研發方向的關聯性:

未來將持續開發測試其他電路區塊的低溫特性,並與超導量子位元整合進行驅動及讀取測試。

團隊針對半導體與超導體量子位元所設計的CMOS電路控制與讀取晶片,包含了數位、類比及射頻的各個電路模塊。