第一列

通用量子電腦硬體技術

邁向高擴充性量子處理器之 CMOS 整合鍺量子位元關鍵技術

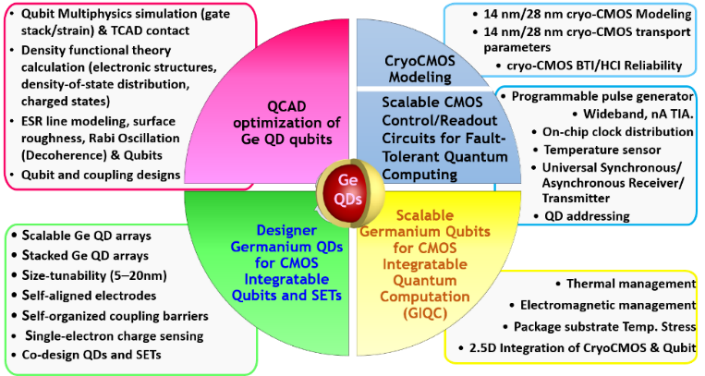

開發CMOS整合高保真量子位元邏輯閘。第一階段: 鍺量子位元之核心元件(如鍺:量子點陣列與電荷感測元件單電子電晶體)以及操控/讀取電路模組等技術開發;第二階段致力於量子計算之次系統量子位元與周邊的操控、讀取以及定址電路之整合。以已開發CMOS製程製作的鍺量子點成長技術為本,製作可調變量子點直徑之鍺量子點陣列,進一步製作量子點量子位元以及電荷感測元件。設計可以對接之低溫金氧半電路以及射頻操控/讀取電路,進行量子位元的狀態疊加、糾纏。研究主題包含:

- 量子點以及量子位元基礎電子能結構以及傳輸行為模擬計算

- 量子位元元件製作

- 量子位元元件晶圓級測量

- 低溫CMOS與射頻操控/讀取電路介面設計

- 輔助電路(定址與溫度監控)

- 量子位元、感測元件以及操控電路、讀取電路之整合。

本計畫之技術願景以及目標

團隊成員

-

共同主持人

-

張懋中(國立陽明交通大學電子研究所)

-

郭建男(國立陽明交通大學電子研究所)

-

唐英瓚(國立中央大學電機工程學系)

技術亮點

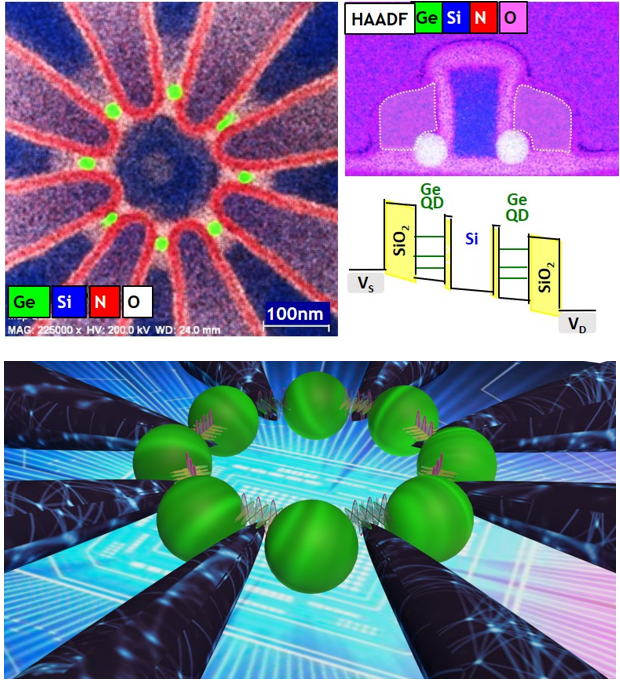

可重組之鍺量子點/矽基位障陣列,適用於高擴充性以及高溫運作之量子位元技術

- 此技術欲解決問題:

具有高擴充性、高重組性以及可高溫運作可行性的鍺量子點陣列製作技術 - 重要性/突破性:

以經典的CMOS製程方法即可以製作出可以精準定位、定數且具有自我組織位障以及自我對準電極的量子位元與電荷偵測器之關鍵結構 - 與計畫未來研發方向的關聯性:

可以CMOS量產技術實踐高擴充性、高溫運作之半導體量子位元

可重組之鍺量子點/矽基位障陣列,適用於高擴充性以及高溫運作之量子位元技術

出處:VLSI Tech. Dig., JFS5-6, pp.1-2, June 2021

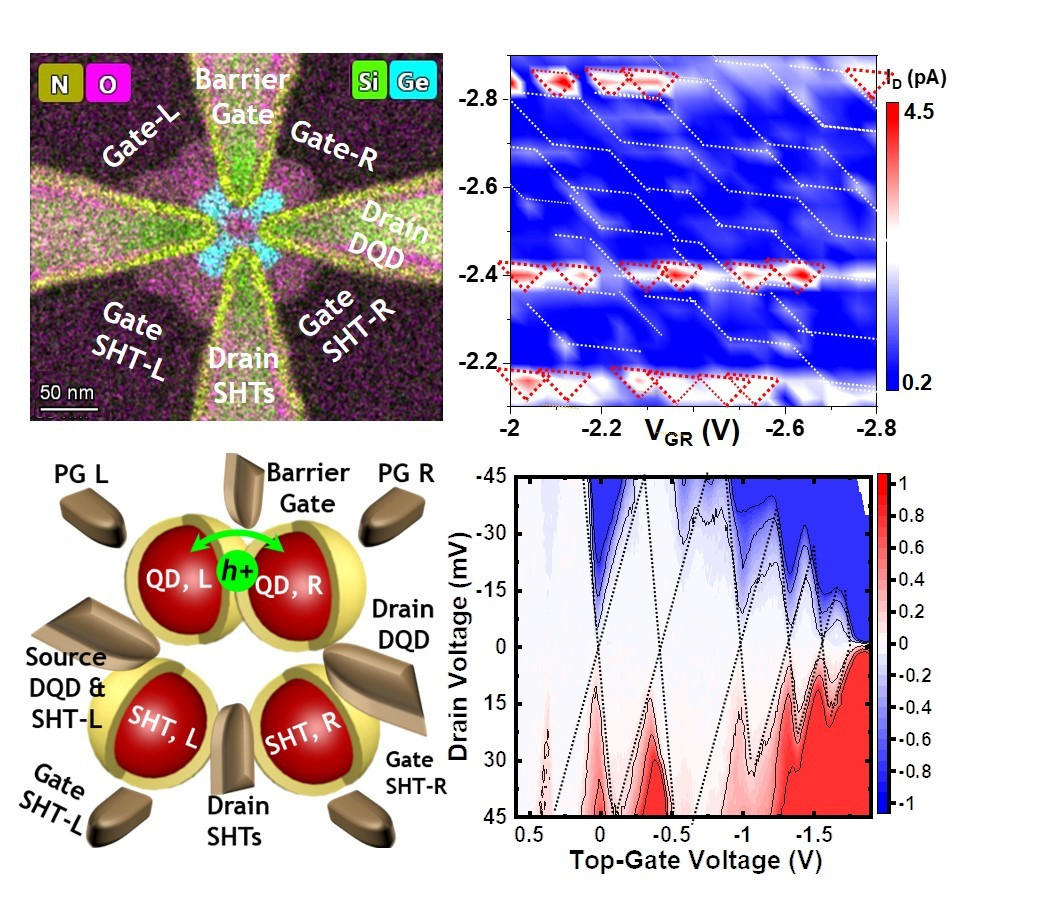

使用直接光電流測量來探測量子點電荷狀態之技術

- 此技術欲解決問題:

需要以複雜的測量技術,方可以決定量子位元電荷狀態之困難 - 重要性/突破性:

在連續光源的照射下,注入少量的光子,可以快速地以直流電性測試方法,決定雙量子點內的電荷狀態。無須製作複雜的匹配電路,也無需使用艱澀的射頻測量技術。 - 與計畫未來研發方向的關聯性:

快速地決定雙量子點的電荷狀態後,可以進一步進行"起始化"、”操控”以及”讀取” 量子位元狀態。

可高溫運作之鍺量子位元與偵測電荷狀態技術

出處:VLSI Tech. Dig., June 2024