第一列

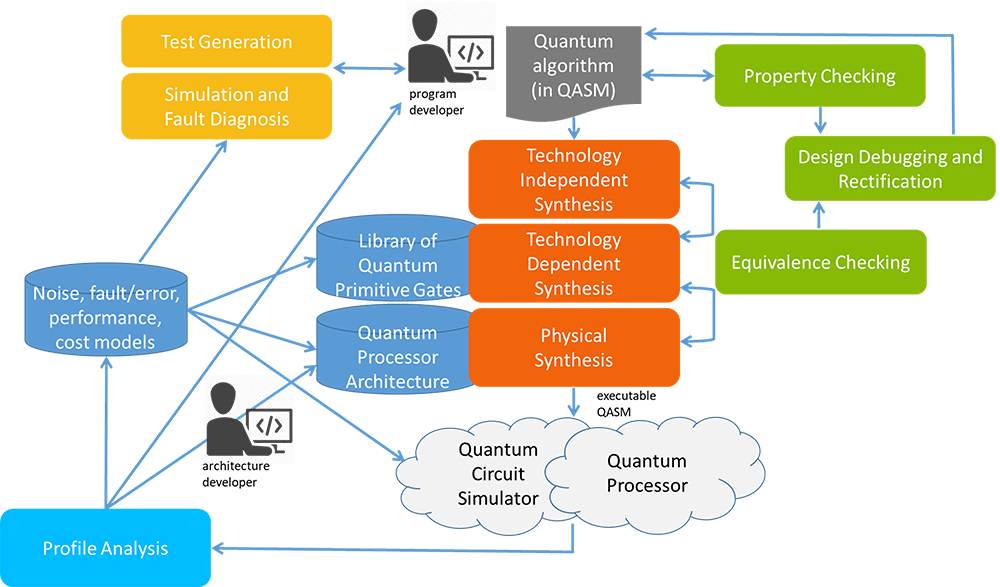

Compiler systems are critical for applications to exploit the potential computational strength provided by the hardware. This project aims to address the problem of quantum software/program compilation for quantum algorithms to be executed on quantum hardware processors. Compiler development requires ample knowledge about the software and the computer architecture so as to analyze and evaluate the hardware-software interactions. This project will build quantum program compilation systems in the directions of quantum program synthesis, simulation, verification, and testing to automate the transformation and optimization of quantum programs in high-level languages to the assembly language executable on quantum processors. Through the domain knowledge of electronic design automation (EDA), we will devise key techniques for synthesizing, simulating, verifying, and testing quantum programs, and develop toolchains for quantum program compilation to bridge quantum application software and processor hardware.

Quantum program compilation systems

-

Co-PI

-

Chien-Mo Li (National Taiwan University)

-

Chung-Yang Huang (National Taiwan University)

Optimizations of Quantum Circuit Simulation for Solving Max-Cut Problems with QAOA

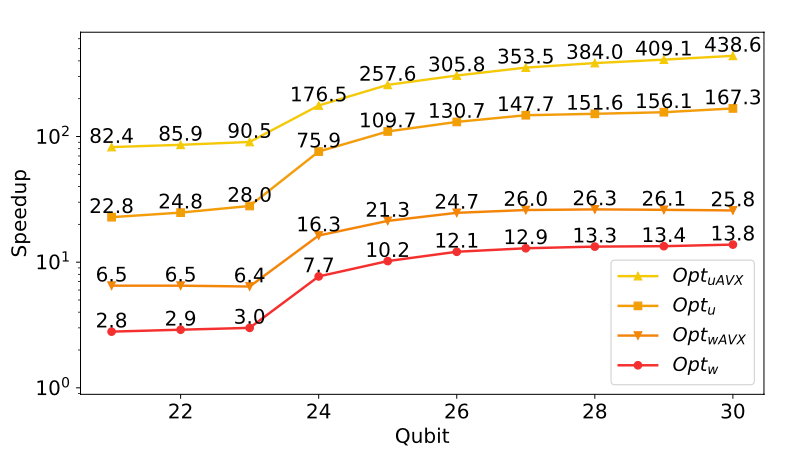

When executing the quantum approximate optimization algorithm (QAOA) on a quantum circuit simulator to solve the combinatorial optimization problem, large-scale computing power is required and the simulation speed is slow. We propose techniques to accelerate quantum circuit simulations (QCS) of QAOA, using mathematical optimization to compress quantum operations, incorporating efficient bitwise operations to further reduce computational complexity, and exploiting the different levels of parallelism of modern multi-core processors , the study case shows the effectiveness of solving the maximum cut problem. Experimental results show significant performance improvements on a virtual quantum computer running a 16-core, 32-thread AMD Ryzen 9 5950X processor, up to 17 times higher than the state-of-the-art simulator QuEST. We believe this work opens new possibilities for accelerating various QAOA applications.

The above figure shows the acceleration effect of the simulated QAOA circuit. The optimization technology we proposed has a significant impact on the simulation performance. In particular, the AVX vector instruction set can process four 64-bit integers at one time to provide nearly four times the acceleration effect.

Reference: Yu-Cheng Lin, Chuan-Chi wang, Chia-Heng Tu and Shih-Hao Hung. TOWARDS OPTIMIZATIONS OF QUANTUMCIRCUIT SIMULATION FOR SOLVING MAX-CUT PROBLEMS WITH QAOA. ACM Symposium on Applied Computing 2024, Avila, Spain, April 8-12.

Boolean Matching of Reversible Logic Circuits

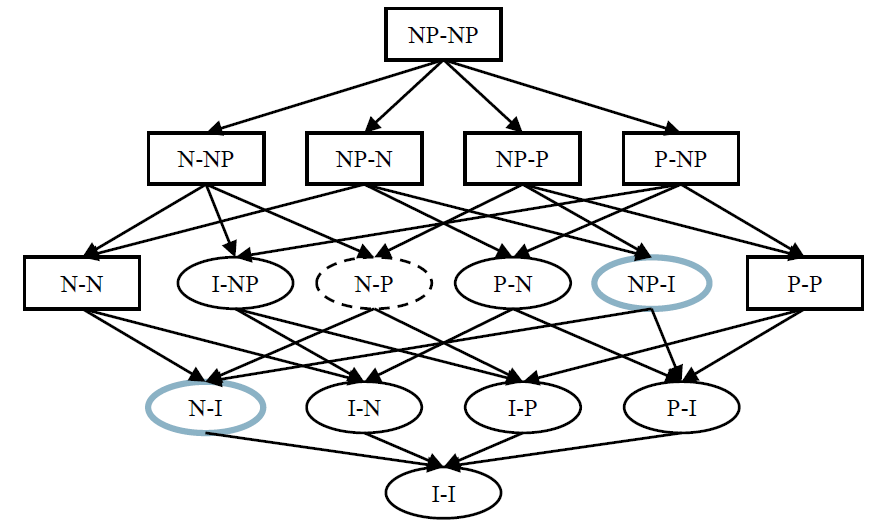

Boolean matching is an important problem in logic synthesis and verification. Despite being well-studied for conventional Boolean circuits, its treatment for reversible logic circuits remains largely, if not completely, missing. This work provides the first such study. Given two (black-box) reversible logic circuits that are promised to be matchable, we check their equivalences under various input/output negation and permutation conditions subject to the availability/unavailability of their inverse circuits. Notably, among other results, we show that the equivalence up to input negation and permutation is solvable in quantum polynomial time, while its classical complexity is exponential. This result is arguably the first demonstration of quantum exponential speedup in solving design automation problems. Also, as a negative result, we show that the equivalence up to both input and output negations is not solvable in quantum polynomial time unless UNIQUE-SAT is, which is unlikely. This work paves the theoretical foundation of Boolean matching reversible circuits for potential applications, e.g., in quantum circuit synthesis.

Dominance relation among various equivalences of Boolean matching for reversible logic circuits. The letter “N” denotes negation equivalence, “P” denotes permutation equivalence, “I” denotes identity, and the symbol “-” aims at separation. The left-hand and right-hand sides of “-” denote the equivalence conditions on the input and output sides of the circuit, respectively. The equivalences in the rectangles are intractable (unsolvable in polynomial time), and those in the oval ones are tractable (solvable in polynomial time). The equivalences in blue ovals require quantum algorithms to achieve tractability when the reverse circuits of the circuits under Boolean matching are unavailable. The equivalence in the dashed oval has unknown quantum complexity when the reverse circuits of the circuits under Boolean matching are unavailable.

Reference: Tian-Fu Chen, Jie-Hong R. Jiang. Boolean Matching of Reversible Circuits: Algorithm and Complexity. In Design Automation Conference (DAC), 2024.

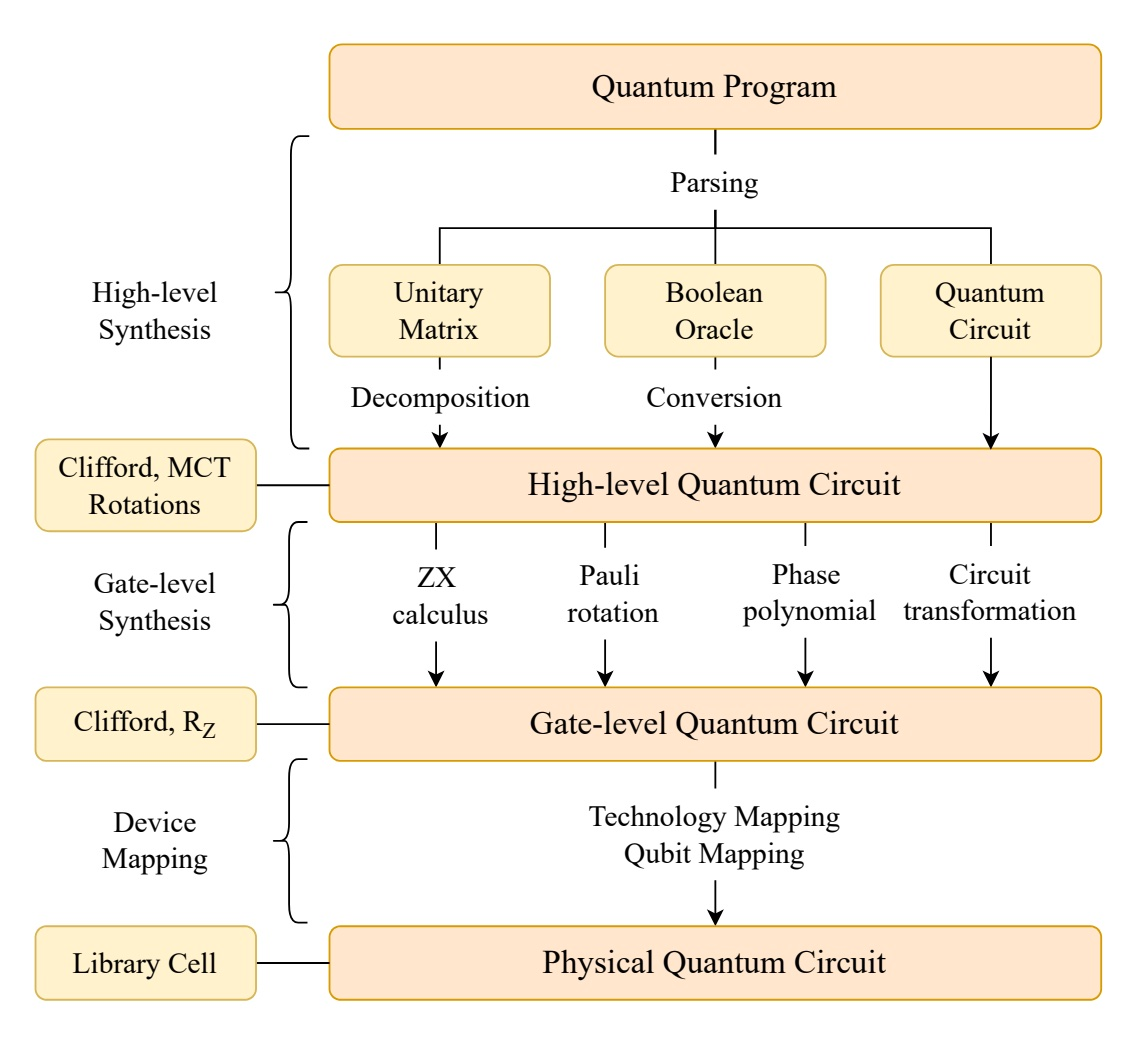

Qsyn: A Developer-Friendly Quantum Circuit Synthesis Framework for NISQ Era and Beyond

Qsyn is an open-source quantum circuit synthesis (QCS) framework to research, develop, and experiment. It is more developer-friendly than other modern QCS frameworks in three aspects: (1) Rich command-line interface for flexible algorithm designs and testing scenarios. (2) Detailed access to many data representations on different abstract levels. (3) Rigid developing environment to ensure development qualities. Besides, the embedded algorithms in Qsyn also outperform other modern platforms.

Qsyn provides a friendly and complete quantum circuit synthesis framework, including high-level, logic-level, physical-level, and small-angle approximated circuit synthesis, etc.

Reference: M-T Lau, C-Y Cheng, C-H Lu, C-H Chuang, Y-H Kuo, H-C Yang, C-T Kuo, H-Y Chen, C-Y Tung, C-E Tsai, G-H Chen, L-K Lin, C-H Wang, T-H Wang, and, C-Y Ric Huang, "Qsyn: A Developer-Friendly Quantum Circuit Synthesis Framework for NISQ Era and Beyond", submitted to IEEE International Conference on Quantum Computing and Engineering (QCE), 2024. (https://arxiv.org/abs/2405.07197)