第一列

A universal quantum computer promises a sustainable ecosystem, fostering advancements in artificial intelligence, drug discovery, exotic materials, and many other fields. Ensuring its reliability, robustness, and scalability is crucial for the successful development of a fully functional quantum computer that will benefit humanity. In this project, we aim to develop a full-stack quantum computer with a 10-qubit quantum processor. We will demonstrate prime number factorization using Shor’s algorithm and molecular simulation with Quantum Phase Estimation on our quantum processor. Additionally, we will perform error detection and mitigation for GHZ state logical qubits. Achieving long coherence time, high readout fidelity, and fault-tolerant gate fidelity are essential for these algorithms. To improve coherence time, we will enhance the internal quality factor of our readout cavity and provide better shielding of qubits from stray fields, infrared, and cosmic radiation. Our commitment to increasing yield by narrowing the spread of Josephson-junction resistance will pave the way for a scalable quantum processor. For better readout fidelity, we will refine our quantum non-demolition readout tools using quantum parametric amplifiers in a single-photon detection scheme. To achieve fault-tolerant gate or control fidelity, we will address this on two fronts: the qubit-processing stack and chip layout. Our modular FPGA-based DAC and ADC will provide picosecond-level phase-locked synchronization between channels, ensuring consistent pulse delivery in line with quantum algorithms, optimized with Randomized Benchmarking. In terms of chip layout, we will develop airbridges to bind the coplanar ground planes, reducing cross-talk and allowing more precise control of X, Y, and Z-gates. Our continuous development of various single-qubit and qubit-qubit gate implementations, such as Hadamard and CZ gates, along with our qubit processing kernel, will ultimately enable our quantum computer to be accessed via the cloud, offering promising applications.

The two-qubit logic gate forms the foundation for logic operations, and - state swap is the most effective way for trimming controlling parameters. A tunable coupler between the two qubits is essential for achieving a high-fidelity two-qubit logic gate. We have achieved a high-quality swap, demonstrating progress in chip design, fabrication, and measurement techniques.

-

Co-PI

-

Yung-Fu Chen (National Central University)

-

Cen-Shawn Wu (National Changhua University of Education)

-

Watson Kuo (National Chung Hsing University)

-

Chung-Ting Ke (Academia Sinica)

-

Yen-Chun Chen (Academia Sinica)

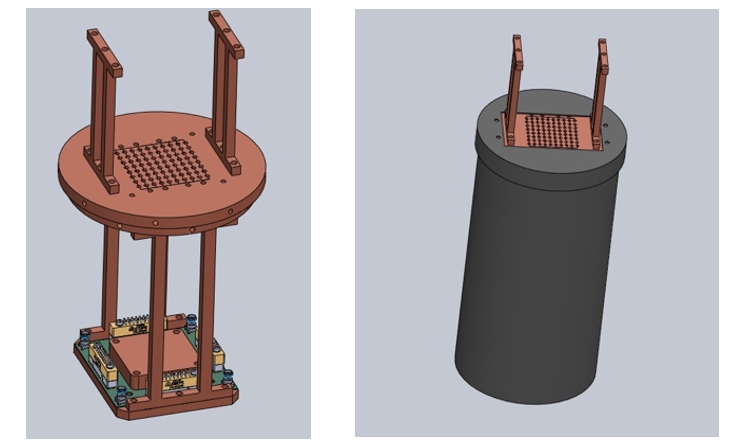

High-quality chip packaging featuring high-density wiring

- A good package should provide absolute protection for the quantum processor(QPU) and faithfully represent the incoming and outgoing signals.

- The basic specifications that have been demonstrated are as follows: Port number=80, microwave crosstalk < -20dB. IR tightening, low flux fluctuations (1/f spectrum density < 10-4 flux quantum)

- The chip package significantly affects the performance of the QPU. With the increasing number of qubits, we will need to develop and produce high-quality packages ourselves.

(Left) A schematic illustrating the structure of high-density packaging.

(Right) A schematic depicting the packaging with infrared shielding and a mu-metal shield.

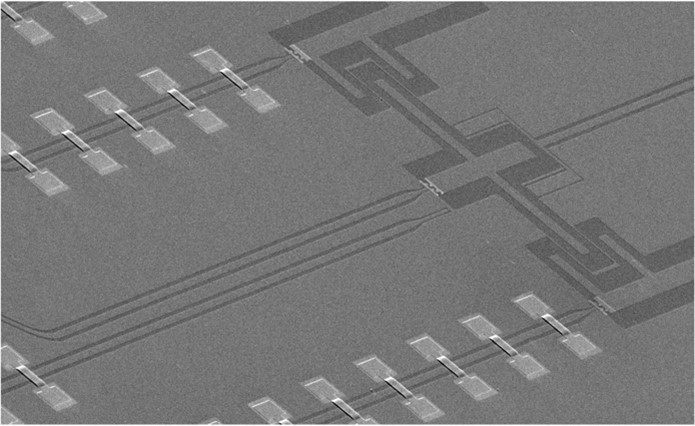

QPU with air-bridges across the coplanar waveguide transmission lines

As the number of qubits grows, crosstalk becomes increasingly prominent. After implementing and validating the air-bridge fabrication process, it was confirmed that qubit resistance remained largely unaffected, demonstrating the feasibility of the current air-bridge method. Air-bridges are crucial for effectively reducing crosstalk, making them essential for multi-qubit chips.

A scanning electron micrograph displays the air bridges, appearing as periodic structures in lighter gray, positioned above the XY-gate and Z-gate signal lines.

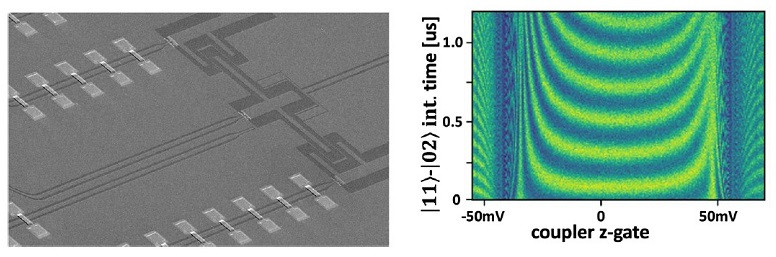

Perfect |11⟩-|02⟩ state swap achieved with tunable coupler technique

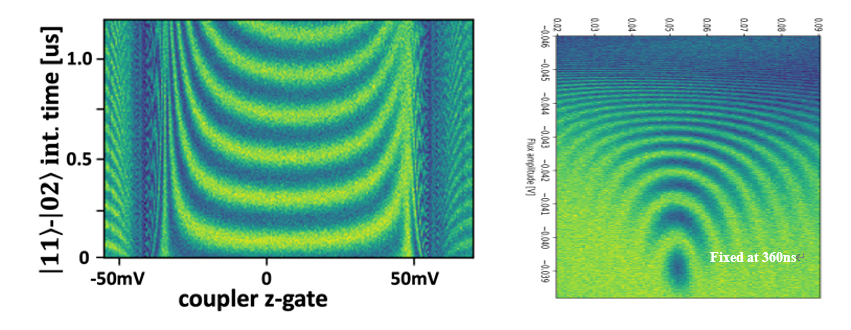

The two-qubit logic gate is essential for executing logic operations, and a tunable coupler between the qubits is key to achieving high-fidelity performance. The |11⟩-|02⟩ state swap is the most efficient method for fine-tuning control parameters. We successfully executed a high-quality swap, highlighting advancements in chip design, fabrication, and measurement techniques.

(Left) |11⟩-|02⟩ state swap as a function of coupler Z bias, clearly showing the off-coupling conditions.

(Right) |11⟩-|02⟩ state swap with a fixed operation time, displayed as a function of qubit frequency and coupler Z bias. These operations enable a continuous set of two-qubit gates.